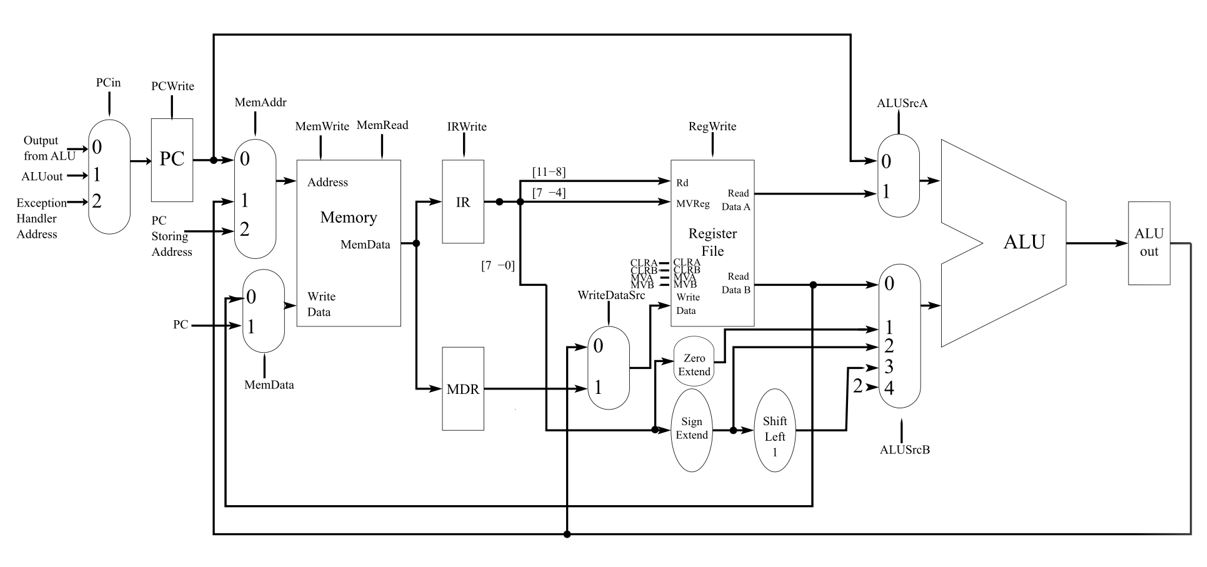

Our architecture is multicycle and is based on a load-store design. Its words, instructions, and register addresses are all 16 bits. The aim of the architecture’s design is to complete instructions quickly and prepare for the next operation at the same time. The A and B registers are used to store the two numbers that the ALU performs operations on. The result of the ALU operations is placed in a temporary register for later use. The architecture supports two instruction formats: DR, which utilizes four control bits to clear or move values in the A and B register, and I, which is used for instructions involving immediates.